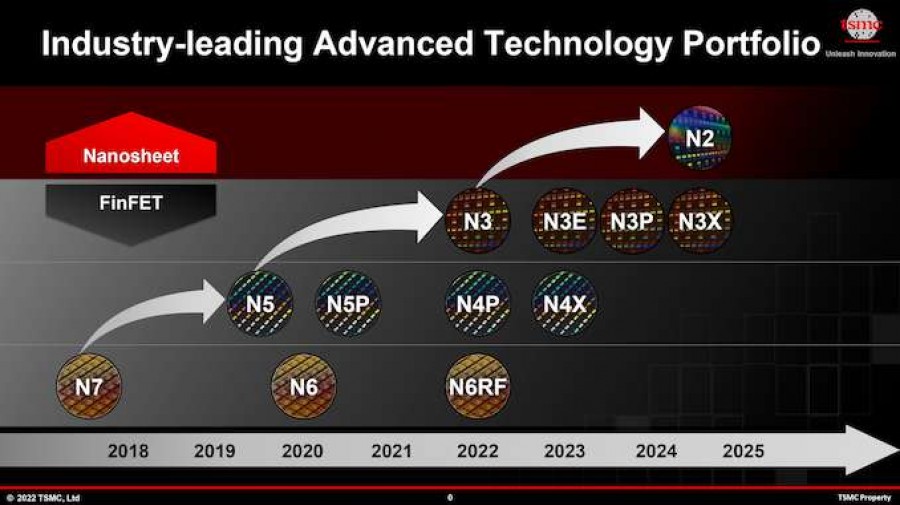

TSMC plant, 3nm im Jahr 2023 und 2nm im Jahr 2025 auf den Markt zu bringen

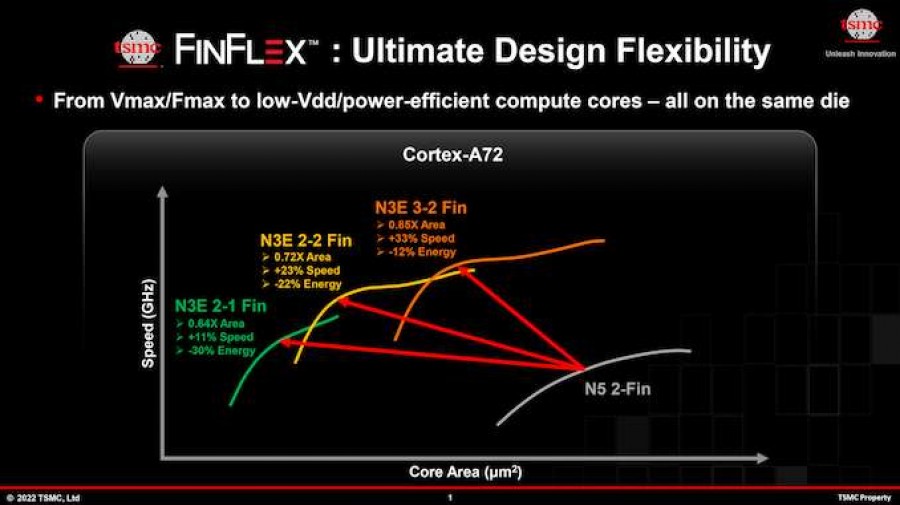

Auf seinem TSMC Technology Symposium 2022 skizzierte TSMC den Zeitplan für seine Chipentwicklung. In der zweiten Hälfte dieses Jahres wird TSMC zum ersten Mal weltweit 3-nm-Chips herausbringen, wobei die 2-nm-Technologie 2025 ihr Debüt geben wird. Es wird fünf Stufen von 3-nm-Chips geben: N3 (Enhanced), N3E (Enhanced), N3P (Erhöhte Leistung), N3S (Erhöhte Dichte) und N3X (Ultrahohe Leistung).

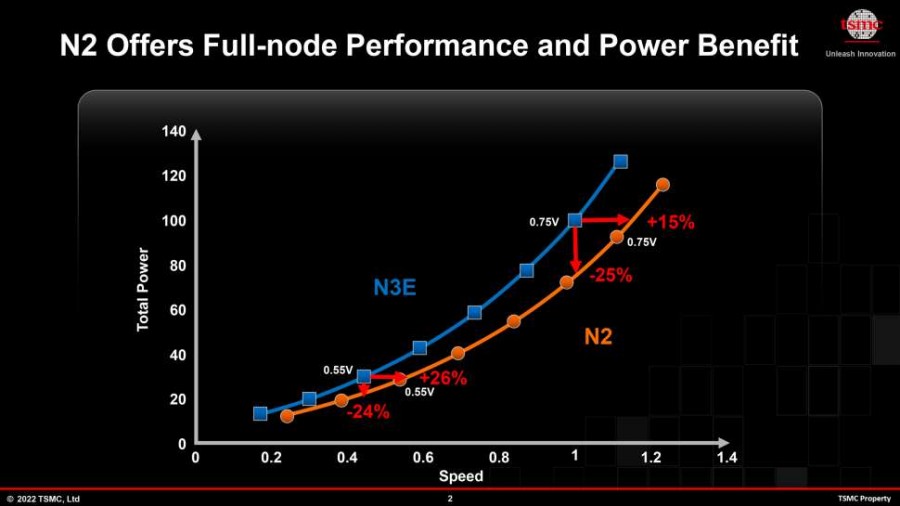

Bei gleicher Leistungsaufnahme verbessert der 2-nm-Knoten die Leistung um 10 % bis 15 % und reduziert den Energieverbrauch um 25 % bis 30 % im Vergleich zur N3E-Generation. Die Chipdichte ist bei N2 höher als bei N3E (1,1-mal).

Außerdem führte TSMC GAAFETs (Gate-All-Around-Feldeffekttransistoren) ein. Die neuen Nanoblatt-Transistoren erhöhen die Leistung pro Watt, indem sie den Widerstand verringern.

Gleichzeitig wird Samsung Foundry im Jahr 2022 auch mit der Massenproduktion von 3-nm-Chips beginnen, und AMD plant, auch im Jahr 2025 mit der Produktion von 2-nm-Chips zu beginnen.

Quelle: www.gsmarena.com