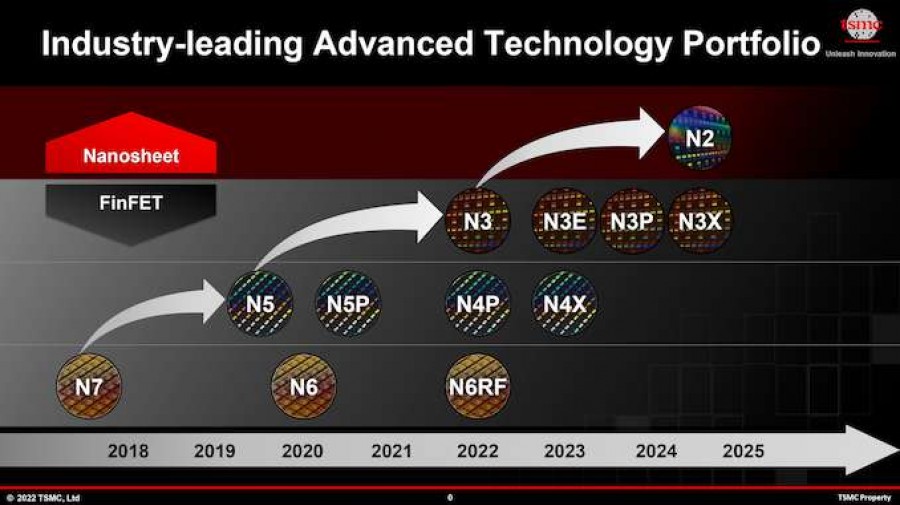

TSMC prévoit de lancer 3 nm en 2023 et 2 nm en 2025

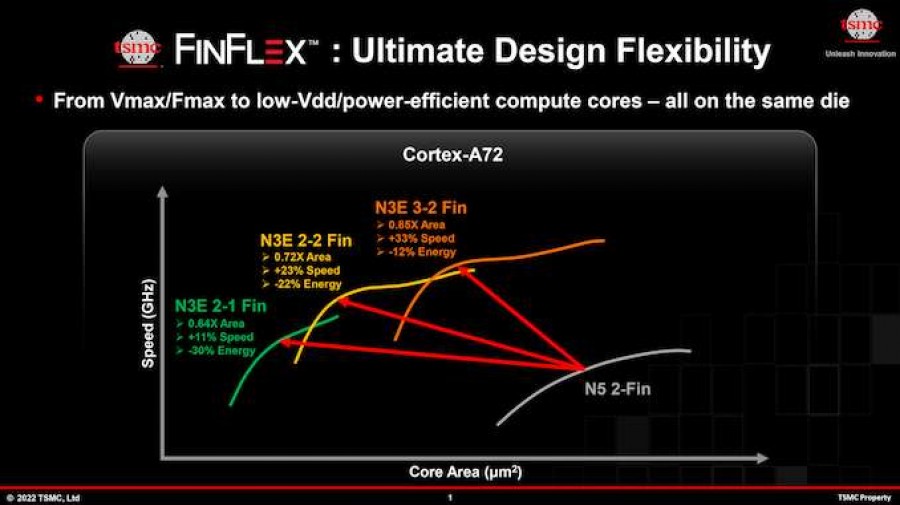

Lors de son symposium technologique TSMC 2022, TSMC a présenté le calendrier de développement de sa puce. Au cours du second semestre de cette année, TSMC lancera des puces 3 nm pour la première fois au monde, la technologie 2 nm faisant ses débuts en 2025. Il y aura cinq niveaux de puces 3 nm : N3 (amélioré), N3E (amélioré), N3P (Performance Enhanced), N3S (Density Enhanced) et N3X (Ultra High Performance).

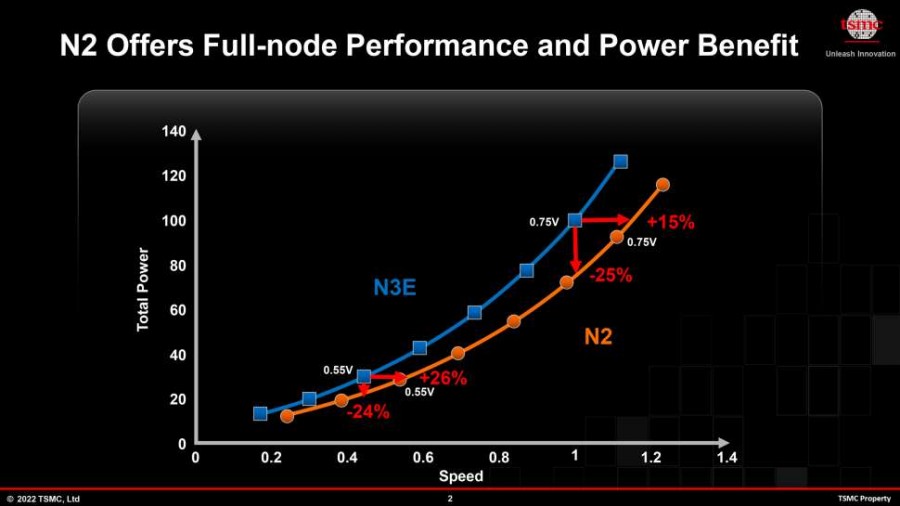

À consommation électrique égale, le nœud 2 nm améliore les performances de 10 % à 15 % tout en réduisant la consommation d'énergie de 25 % à 30 %, par rapport à la génération N3E. La densité de copeaux est plus élevée avec N2 qu'avec N3E (1,1 fois).

En outre, TSMC a introduit les GAAFET (transistors à effet de champ tout autour de la porte). Les nouveaux transistors à nanofeuilles augmenteront les performances par watt en réduisant la résistance.

Dans le même temps, Samsung Foundry commencera également à produire en masse des puces 3 nm en 2022, et prévoit également de commencer à produire des puces 2 nm en 2025.

Source: www.gsmarena.com